# UNIC-CASS Design-to-Tapeout Meetup #2 (Aug. 28, 2024)

# Digital and analog design flows

Presented by: D-to-T mentoring team

**Design-to-Tapeout Mentoring** Communication and organization

- Bi-weekly mentoring sessions

- Slack Channel

- **UNIC-CASS** website

**UNIC-CASS Slack channel:** https://unic-cass.slack.com/

Universalization of IC Design From CASS (UNIC-CASS)

#### **Universalization of IC Design from CASS** (UNIC-CASS)

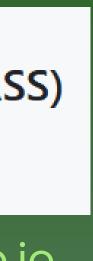

The Universalization of IC Design from CASS (UNIC-CASS) program is a structured end-to-end Integrated Circuit (IC) design-to-test experiential learning. The program aims to improve the know-how and accessibility to IC Design technologies for enthusiasts and design communities worldwide in low-to-middle-income and/or low-opportunity countries. This program is of strategic cooperation with the Solid-State Circuits Society serving geographicalcomplementing locations.

O UNIC-CASS Mentoring Session Recordings & Presentations

The IEEE Circuits and Systems Society (CASS) invites you to participate in the Universalization of IC Design from CASS (UNIC-CASS) program, a structured end-to-end Integrated Circuit (IC) design-to-test experiential learning. The program aims to improve the know-how and accessibility to IC Design technologies for enthusiasts and design communities worldwide in low-to-middle-income and/or low-opportunity countries. This program is of strategic cooperation with the Solid-State Circuits Society serving geographical-complementing locations.

There are no restrictions to designing your ideal chip on design complexity or type (digital, analog/RF, or mixed-signal). Based on the quality of their submitted chip design proposals, selected participants will get the opportunity to learn from carefully curated materials on the CASS MiLe platform, hands-on design mentoring by experts in the field, submit designs to CASS-sponsored fabrication runs via Efabless chipIgnite program and test your fabricated chip at selected testing facilities.

UNIC-CASS Mentoring Session Recordings & Presentations

Recordings and presentations: <u>https://ieee-</u> cas.org/unic-cass-mentoring-sessionrecordings-presentations

### UNIC-CASS educational material

- New videos made by volunteers following the lecture notes

- Lecture notes in Markdown format  $\bullet$  $\Rightarrow$  You can contribute by updating them

- New document theme using Just-the-docs Jekyll theme

- Latest materials in Github

- Materials in CASS-MiLe will be updated into v2.0 soon

- Add instructions for Klayout in analog design flow •Layout Universalization of IC Design from CASS Universalization of IC Desig... + Q Search courses •DRC •LVS

#### Universalization of IC Design from CASS (UNIC-CASS)

A 9 followers 2 https://ieee-cas.org/universalization-i...

#### Source: <u>https://github.com/unic-cass/unic-cass.github.io</u>

Universalization of IC Design in CASS

#### Home

#### Course introduction

- 1.1 Introduction to the course

- 1.2 Introduction to PDKs

- 1.3 Introduction to the Digital **Design Flow**

1.4 Introduction to Analog Design Flow with opensource tools

- **Environment Setup**

- Analog Design Flow

- **Digital Design Flow**

Preparing the design for tapeout

#### Design examples

#### 1. Course Introduction

Q Search Universalization of IC Design in CASS

#### TABLE OF CONTENTS

- 1.1 Introduction to the course

- 1.2 Introduction to PDKs

- 1.3 Introduction to the Digital Design Flow

- 1.4 Introduction to Analog Design Flow with openso

Copyright © 2024 IEEE CASS

Edit this page on GitHub.

#### Website: <u>https://unic-cass.github.io</u>

Working

Course

UNICASS 6 -**Preparing the** (guided by Efabless)

Design exam

#### CASS-MILE:

| ource tools |

|-------------|

|             |

|             |

|             |

### **Design-to-Tapeout Mentoring Team 2024**

#### Gabriel Maranhão, UFSC (Brasil)

#### Deni Alves UGA (France)/UFSC (Brasil)

Jorge Marin UTFSM (Chile)

#### Francisco Brito UFERSA (Brasil)

#### Duy-Hieu Bui, VNU Hanoi (Vietnam)

Sergio Bampi UFRGS (Brasil)

### Main Design-to-tapeout milestones

First design review (mock tapeout) Purpose: Prepare the teams in advance for the final tape-out phase Date: Last week of September Second design review (first DRC/LVS clean design delivery) Purpose: Verify feasibility of designs and top integration Date: Second week of October UNIC-CASS tapeout Purpose: final delivery of top designs Date: November 8<sup>th</sup>

## Design-to-Tapeout Mentoring Weekly mentoring sessions 1

| Activities                                  | Date/<br>Deadline                         | Purpose/ comments                                                                                                                                      | Your Deliverables<br>(provide info/links<br>on your GitHub) | We will<br>provide/handle                                                          |

|---------------------------------------------|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|------------------------------------------------------------------------------------|

| 1st Meet-up                                 | Aug 12, 1pm-2pm<br>UTC                    | Kick-off meeting                                                                                                                                       | N/A                                                         | N/A                                                                                |

| Weekly meet-ups                             | 21/8,28/8,4/9, 18/9<br><b>1pm-2pm UTC</b> | Mentoring and Design groups to<br>present progress.<br>Short presentations on topics<br>such as Caravel/Caravan, best<br>practices, pitfalls to avoid. | N/A                                                         | Slides and videos will be<br>posted on the UNI-CASS<br>website                     |

| 1st Design<br>submission [Mock<br>tape-out] |                                           | Prepare the teams in advance for the final tape-out phase                                                                                              | Passing pre-check report                                    | <ol> <li>Detailed instructions for<br/>pre-check</li> <li>Example files</li> </ol> |

| 1st Design Review &<br>Feedback             | Oct 2                                     | Provide feedback and advice for the next stages                                                                                                        | N/A                                                         | Feedback on the pre-<br>check work                                                 |

| Weekly meet-ups                             |                                           | Focused mentoring +<br>preparation for final tape-out +<br>evaluate status of potential drop-<br>outs                                                  | N/A                                                         | Slides and videos will be<br>posted on the UNI-CASS<br>website                     |

## Design-to-Tapeout Mentoring Weekly mentoring sessions 2

| Activities                                      | Date/<br>Deadline | Purpose/ comments                                 | Your Deliverables<br>(provide info/links<br>on your GitHub)                                                      | We will<br>provide/handle                                                                                                     |

|-------------------------------------------------|-------------------|---------------------------------------------------|------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| 2nd Design<br>submission                        | Oct 16            | Verify feasibility of designs and top integration | Detailed circuit description<br>(pinout, area and<br>functionality) + DRC/LVS<br>reports on Efabless<br>platform | Check reports to confirm all blocks are LVS and DRC clean.                                                                    |

| 2nd Design Review<br>& Feedback from<br>mentors | Oct 23            | Provide feedback and advice for the final stages  | N/A                                                                                                              | Feedback on the individual designs + advice for top merge                                                                     |

| Efabless pre-check<br>+ tapeout                 |                   | Complete tape-out work on<br>Efabless platform    | Deliver COMPLETE<br>Caravel/Caravan drop-ins<br>to Efabless final check                                          | Provide assitance to tape-<br>out leaders within the<br>teams                                                                 |

| Tape-out                                        | Nov 11            | See:<br>https://efabless.com/chipignite           | N/A                                                                                                              | List of winner teams<br>included in this tapeout<br>List of unfinished designs to<br>candidate for 2025 UNIC-<br>CASS program |

| Chip delivery date                              |                   | See:<br>https://efabless.com/chipignite           | N/A                                                                                                              | Chip shipping and testing logistics                                                                                           |

### Additional remarks I

### Firm deadlines!

- and reviews (see schedule)

- - A working design based on open source IP for analog

- Working Verilog code with the main functionality for digital

- platform: https://platform.efabless.com/projects/public

- Also, join the OSS slack channel: https://join.skywater.tools

November 11 is the hard tapeout date provided by Efabless Please plan according to the proposed activities: design submission

Define a "minimum viable product" as soon as possible, e.g.:

For inspiration: Open source designs – public projects in the efabless

### Additional remarks II

**UNIC-CASS uses multi-block caravels** Area and pin count are limited for each project Exact numbers will be adjusted as we see progress Minimize merge work as much as possible

## Additional remarks III

### Finalizing the design is not the finishing line!

- Efabless pre-checks

- Tapeout checks

- - Allocate extra time to understand and execute this

- Mock tapeout!

Based on previous experience, some issues can arise at these steps

### **Current actions by design teams**

#### Get the OS design tools working

- Instructions available in UNIC-CASS educational material website: https://uniccass.github.io/training/02-env-setup.html

- Example: docker version with all the tools you need  $\rightarrow$  https://github.com/iicjku/IIC-OSIC-TOOLS

- Start your design  $\rightarrow$  define your "roadmap"

- Distribute tasks among members (e.g. analog/digital, schematic/layout, etc.) Define concrete building blocks and their specifications

- Create testbenches and get started with simulations

# UNIC-CASS Design-to-Tapeout Meetup #2 (Aug. 28, 2024)

# Introduction to the Opensource Analog Design Flow Presented by: Jorge Marín, Research Associate, AC3E-USM

### INTRODUCTION

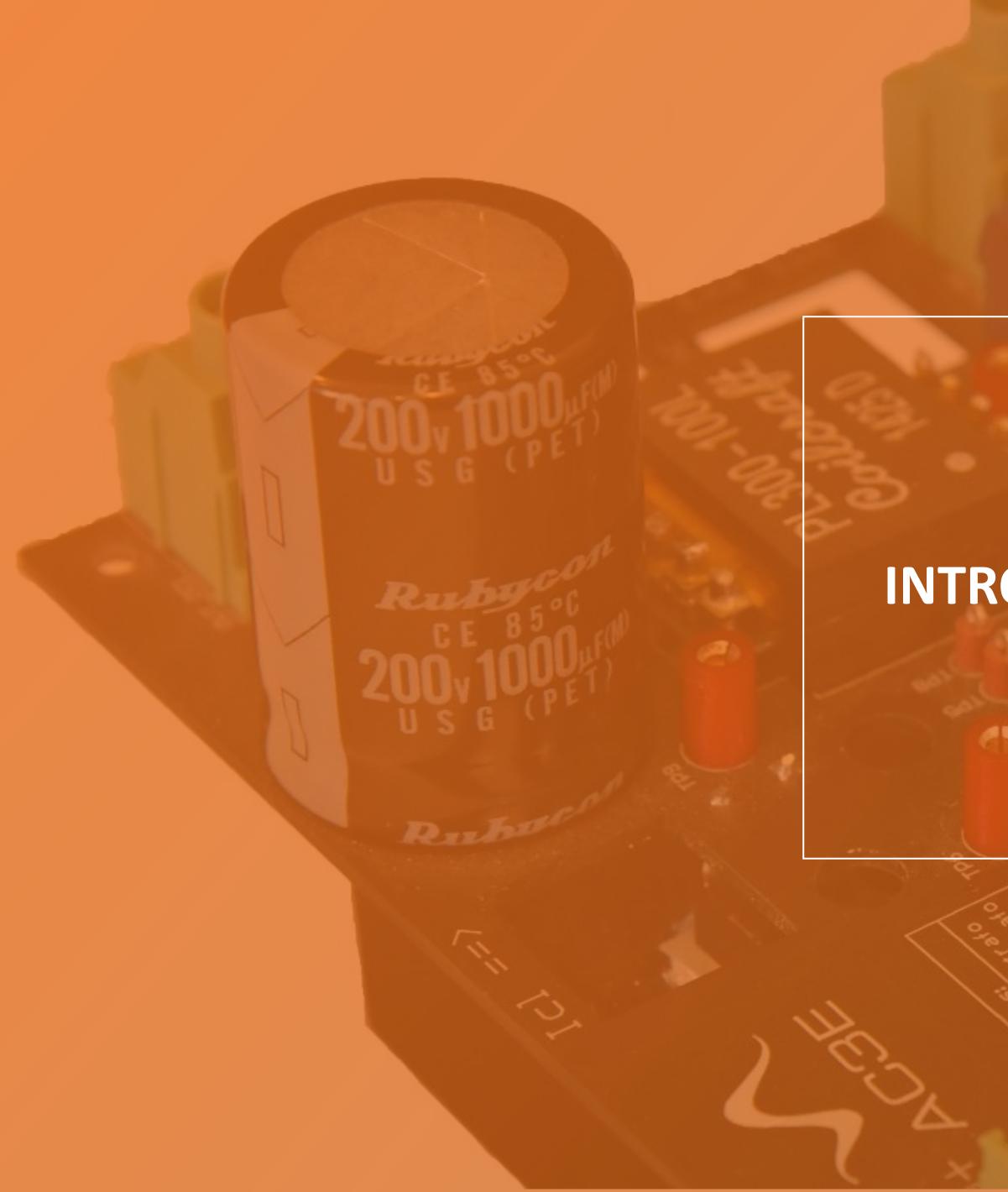

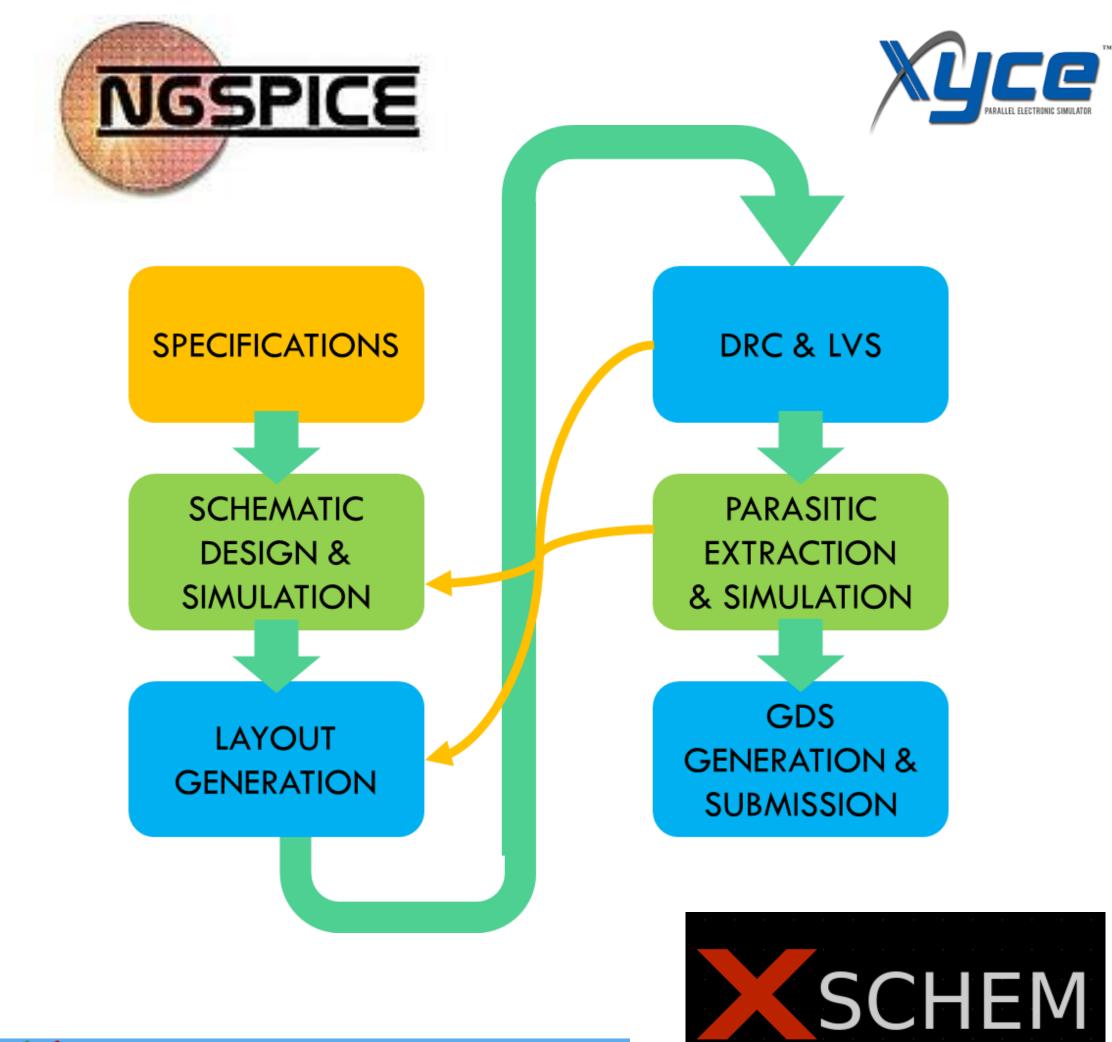

# Analog vs digital design flows

## **OPENSOURCE EDA TOOLS**

FLOV **DIGITA**

J **ANALO**

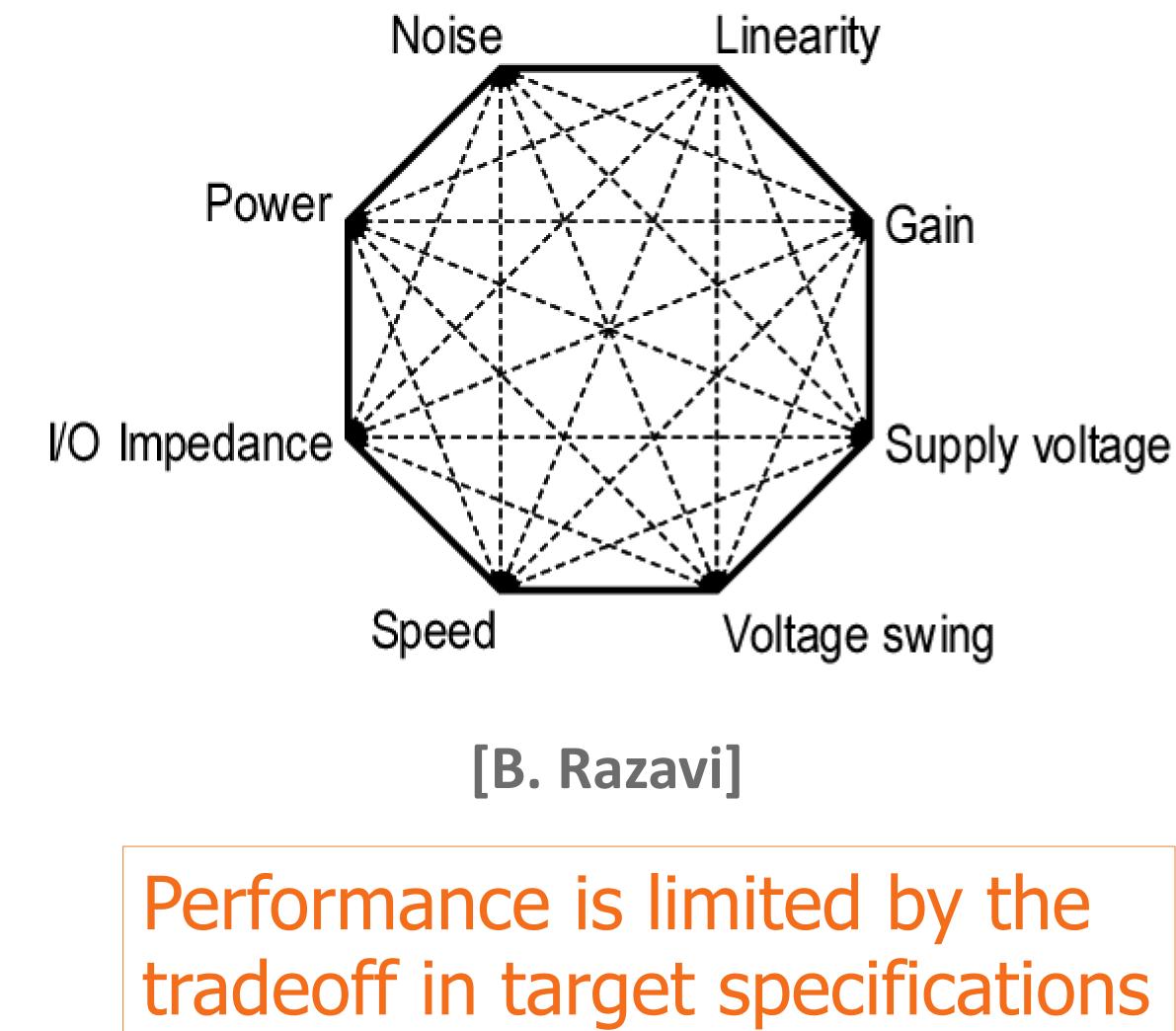

# Tradeoffs in analog design

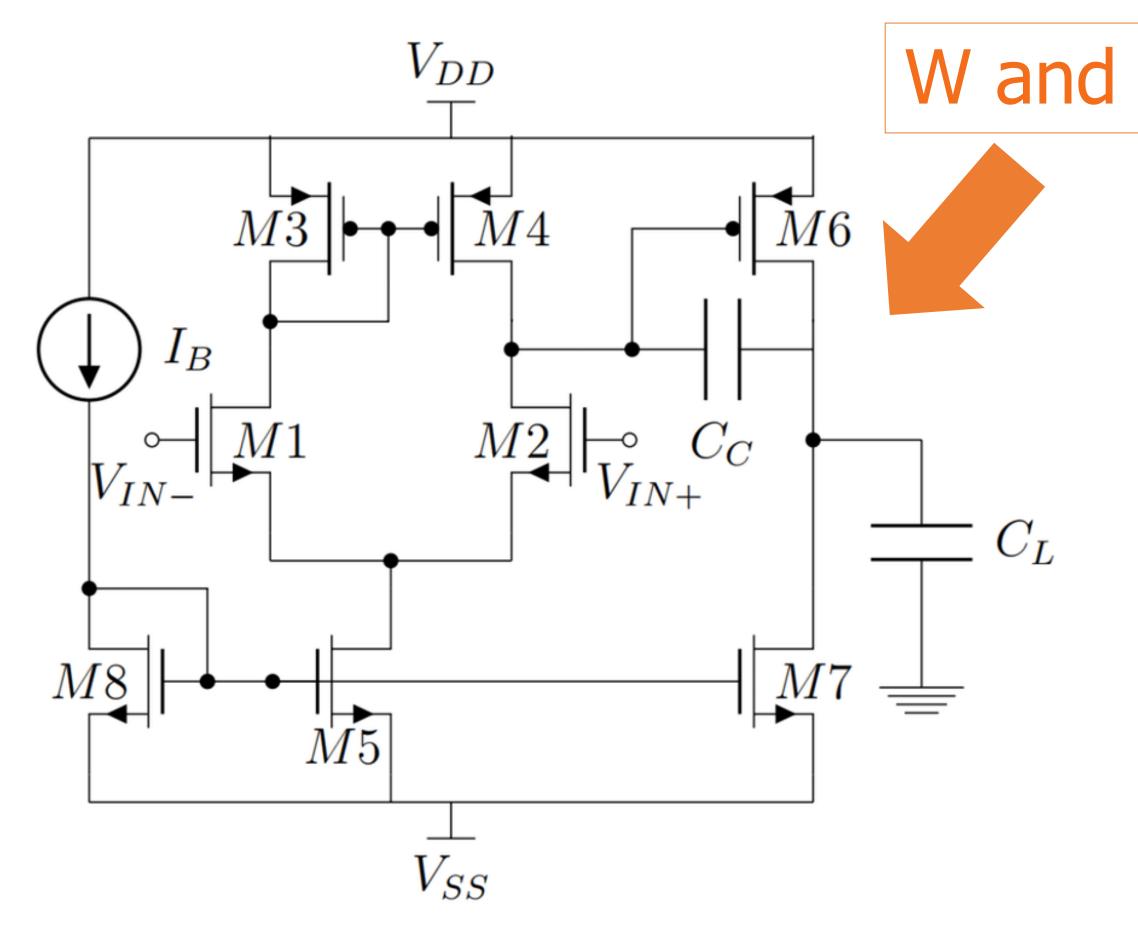

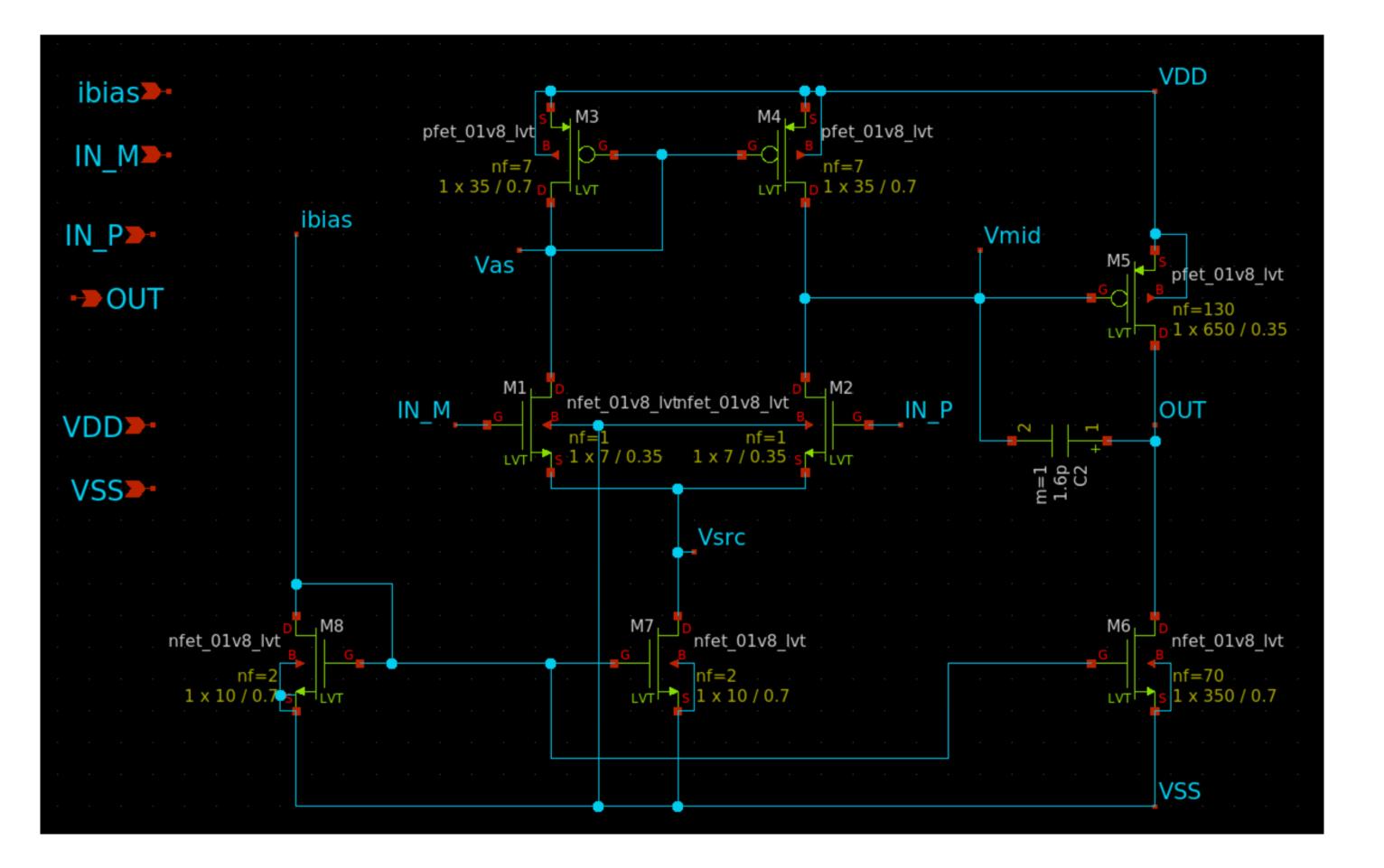

**Analog block example: Miller OTA**

### W and L for each transistor M1 to M8?

#### BASIC USE OF ANALOG TOOLS

# Analog design flow environment setup

## How to get started with design and simulation?

- Environment setup

- Option 1: Analog Mixed Signal Design using docker image & remote desktop

- e.g. IIC-OSIC-TOOLS docker Clone at: https://github.com/iic-jku/iic-osic-tools Follow detailed instructions

- Option 2: Analog Mixed Signal Design tools on Linux or WSL using Conda

See the environment setup material in the UNIC-CASS page: https://unic-cass.github.io/training/02-env-setup.html

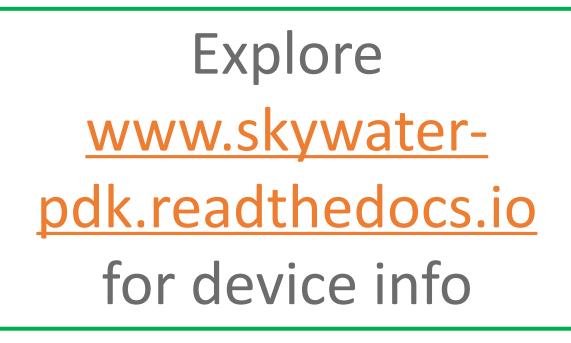

# Schematic design and simulation

- Relevant tools

- Xschem

Schematic entry and netlist generation

- Visualization

- Ngspice window  $\rightarrow$  quick checks

- GAW → integrated in Xschem

- External viewer through raw data (e.g. Python script)

# • Ngspice $\rightarrow$ simulation based on netlist generated by Xschem

# Simulation types

- Simulation types

- DC  $\rightarrow$  operating point

- AC  $\rightarrow$  frequency sweep

- Transient  $\rightarrow$  time-domain behavior

- Noise  $\rightarrow$  simulation of device intrinsic noise

- And others...

### Ngspice manual will become your best friend! https://ngspice.sourceforge.io/docs/ngspice-manual.pdf

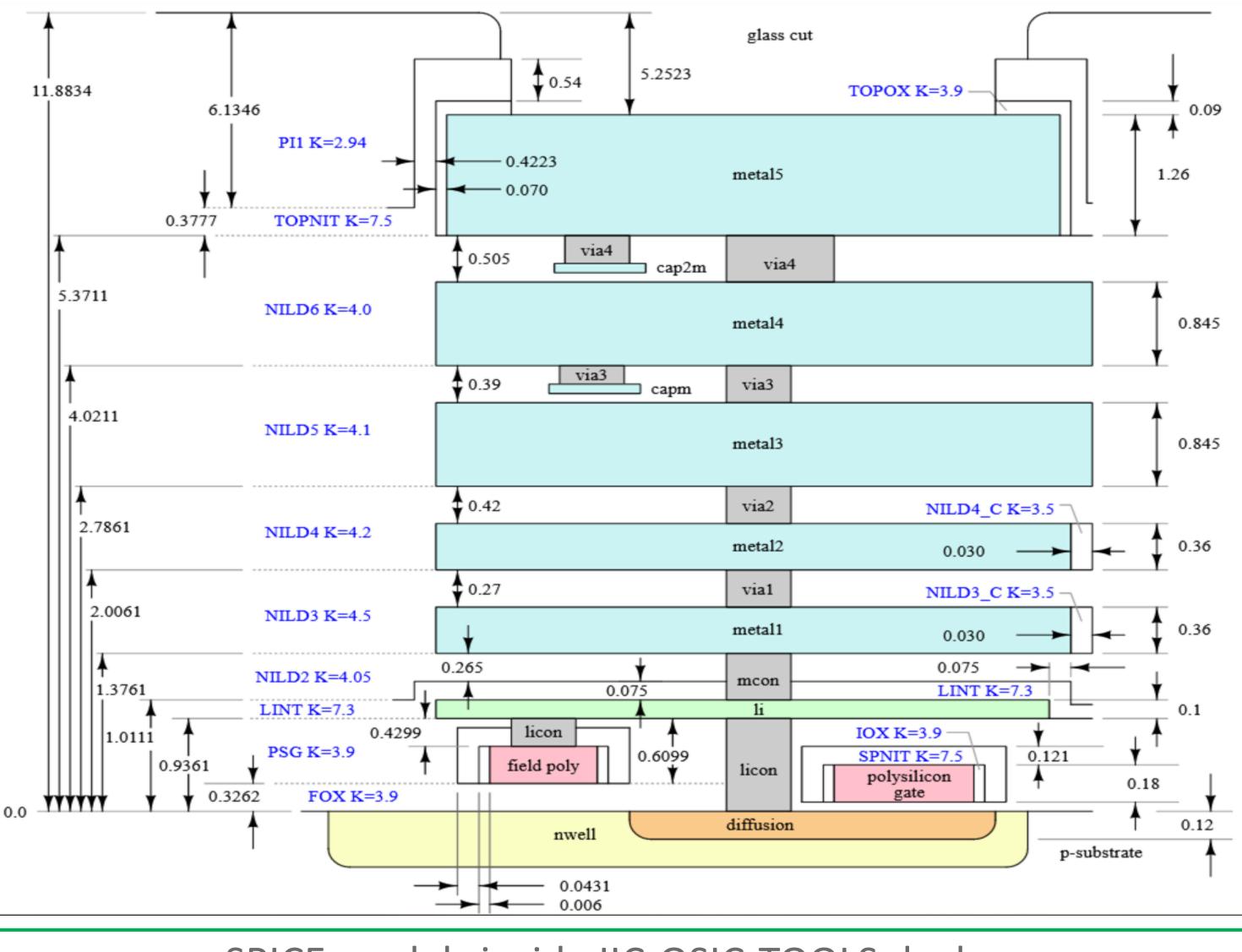

## Available devices in SKY130

SPICE models inside IIC-OSIC-TOOLS docker: .lib /foss/pdks/sky130A/libs.tech/ngspice/sky130.lib.spice tt

#### **Device Details**

#### 1.8V NMOS FET

#### Spice Model Information

- Cell Name: sky130\_fd\_pr\_\_nfet\_01v8

- Model Name: sky130\_fd\_pr\_\_nfet\_01v8

Operating Voltages where SPICE models are valid

- $V_{DS} = 0$  to 1.95V

- $V_{GS} = 0$  to 1.95V

- $V_{BS} = +0.3$  to -1.95V

## Xschem GUI

| ʻc'<br>ʻq'<br>ʻa'<br>ʻin |          | copy<br>open object query window<br>auto symbol creation<br>open insert device window |

|--------------------------|----------|---------------------------------------------------------------------------------------|

| 'q'                      |          | open object query window                                                              |

| 140 A.C. 140 - 5         |          |                                                                                       |

| <b>'</b> C <b>'</b>      |          | сору                                                                                  |

|                          |          |                                                                                       |

| ʻu'                      |          | undo                                                                                  |

| <b>'</b> SH              | HFT + r' | rotate                                                                                |

| <b>'A</b> L              | LT + f'  | flip                                                                                  |

| 'm                       |          | move element                                                                          |

| <b>'</b> W'              |          | draw wire                                                                             |

www.xschem.sourceforge.io

nt Simulation

### DE1-04709,"."

#### Generate netlist

#### **Execute simulation**

#### Check waveforms (GAW)

ouse = 40 -630 - selected: 0 path: .X1.

# Simulation scope

- Nominal

- P(VT) corners

Considers global process variation (P) and environment (Voltage, temperature, T)

.lib /foss/pdks/sky130A/libs.tech/ngspice/sky130.lib.spice tt

Mismatch

**Considers local statistical variation among devices**  $\rightarrow$  See example: https://unic-cass.github.io/training/7.7design-examples-xschem-ngspice-mc-sim.html Parasitic extraction/ post layout simulations Components associated to extrinsic structures (metallization)

### Ideal simulation without considering many fabrication effects

# CACE: Circuit Automatic Characterization Engine

- Allows to run Montecarlo, corner sweeps and post-layout simulations in a structured way

- Usage and examples: <u>https://github.com/efabless/cace</u> Documentation: <u>https://cace.readthedocs.io/en/latest/</u> See also the "cace" channel in the OSS Slack

- "CACE Study: Open source analog and mixed-signal design flow" -Tim Edwards (Latch 2024): https://youtu.be/0UMb-vd4MtU?si=4eZUPfScApC2MfHf

### EXAMPLES

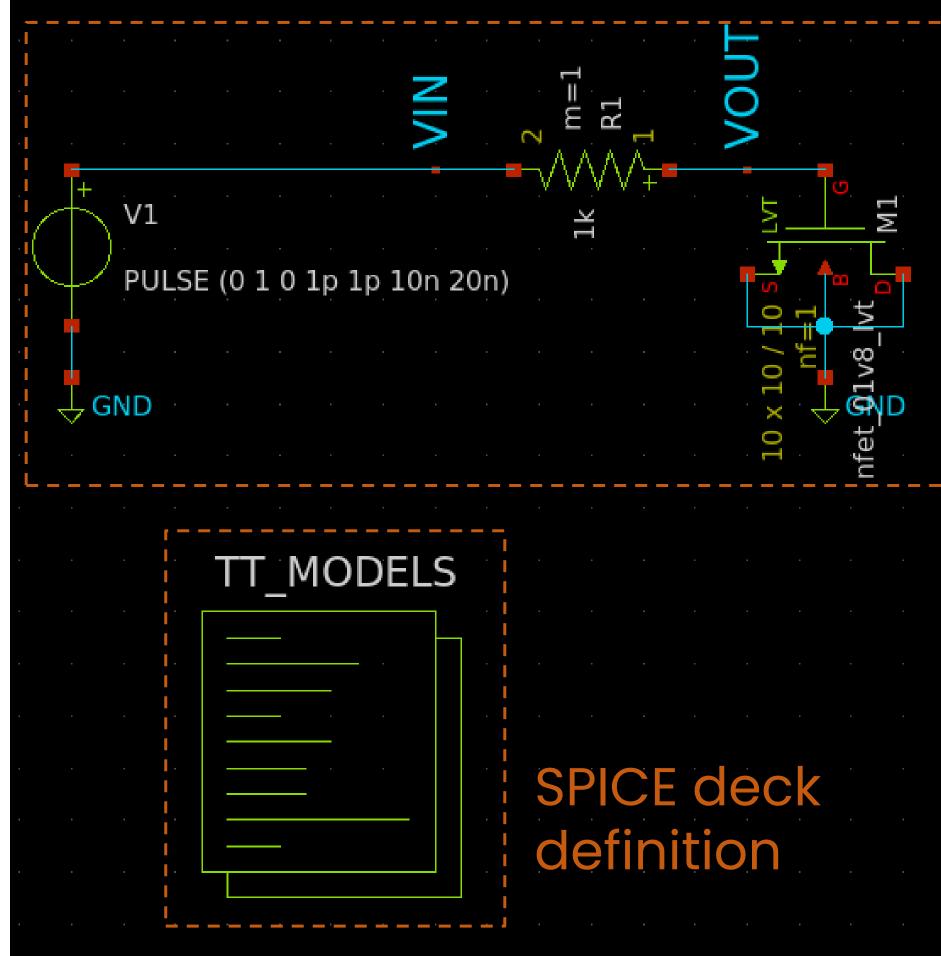

### Example #1: Basic inverter

# An inverter schematic in **Xschem with** Skywater 130nm

Check video tutorial: https://unic-cass.github.io/training/3.1.3-schematiccapture-inverter.html

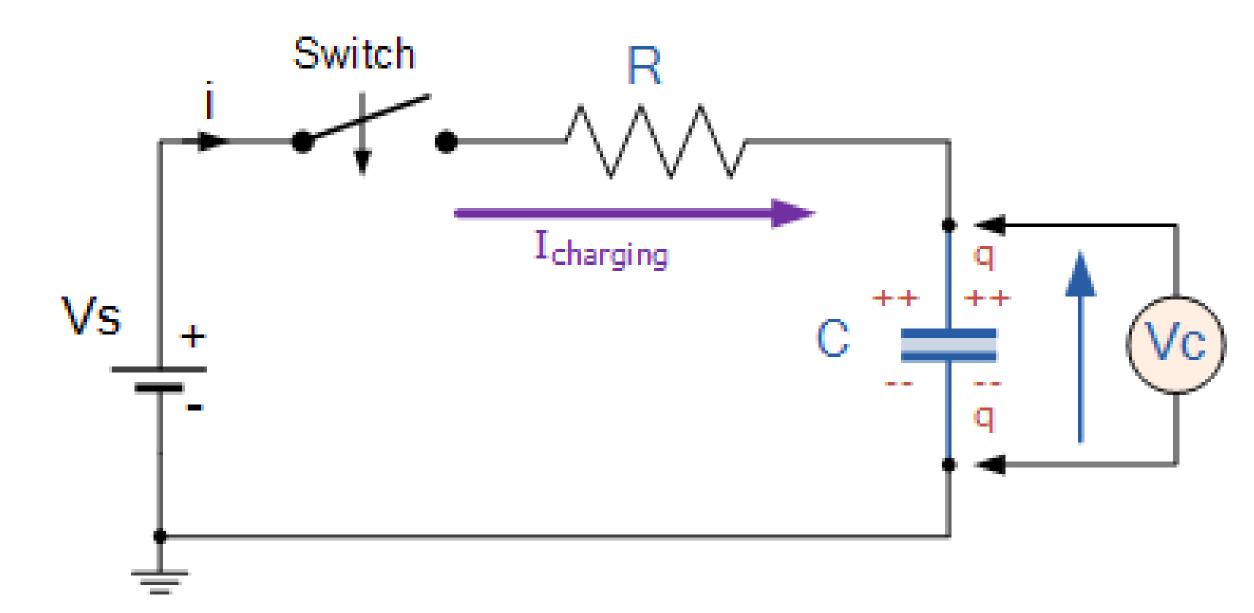

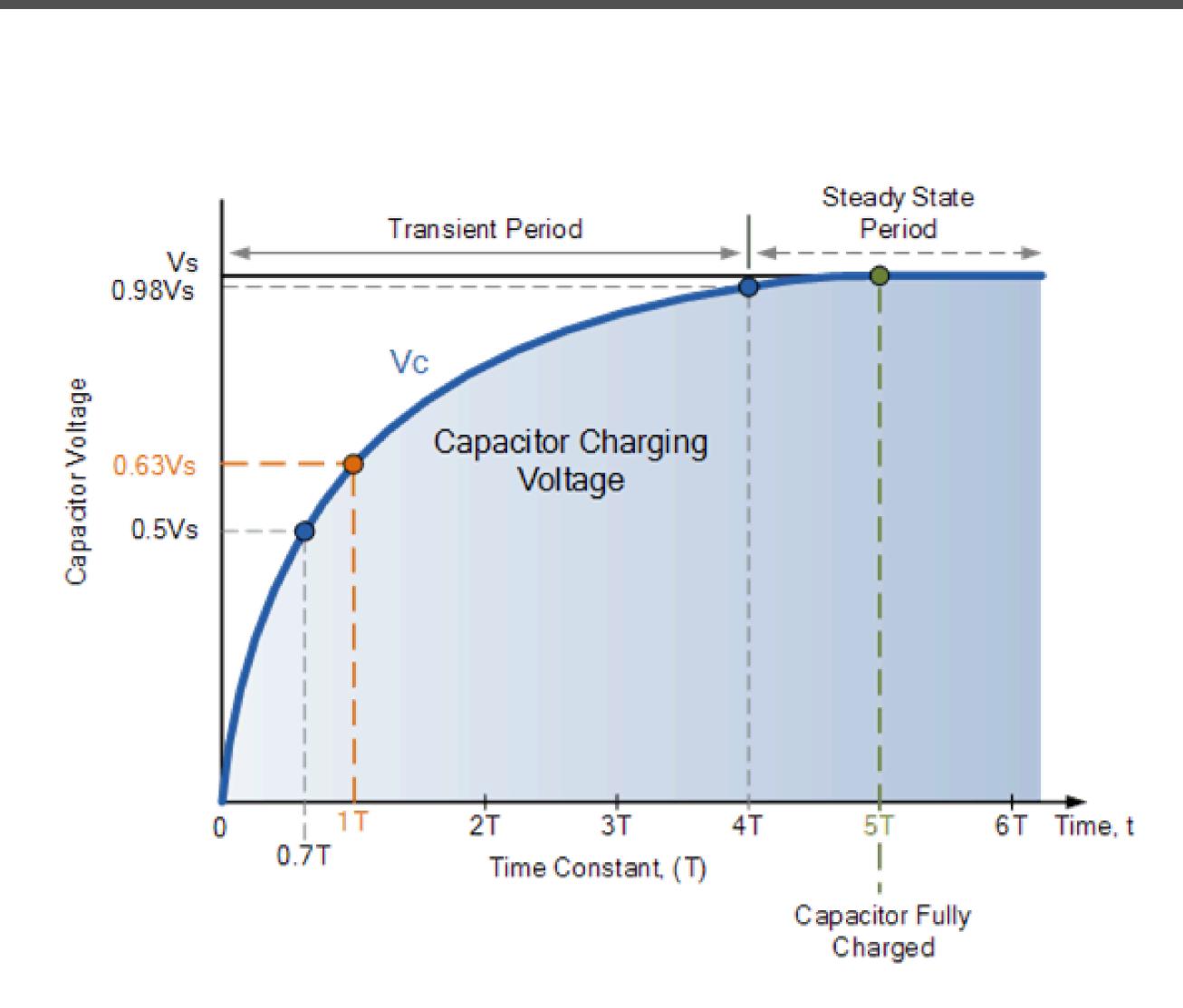

# Example #2: RC constant calculation

Source: https://www.electronics-tutorials.ws/rc/rc\_1.html

# Example #2: RC constant calculation

### • Github link:

https://github.com/JorgeMarinN/UNIC-CASS2024\_AnalogOSIC/blob/main/cgate-ext\_circuit\_UNIC-CASS2024.sch

| <pre></pre>                                                                                                                                                                                                 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <pre>.tran 100p 20n<br/>.save all<br/>.ic v(vout) = 0<br/>.control<br/>run<br/>meas tran teval WHEN v(vout) = 0.63<br/>let res_val = 1000<br/>let cap_val = teval/res_val<br/>print cap_val<br/>.endc</pre> |

| Simulation/measurement<br>SPICE code                                                                                                                                                                        |

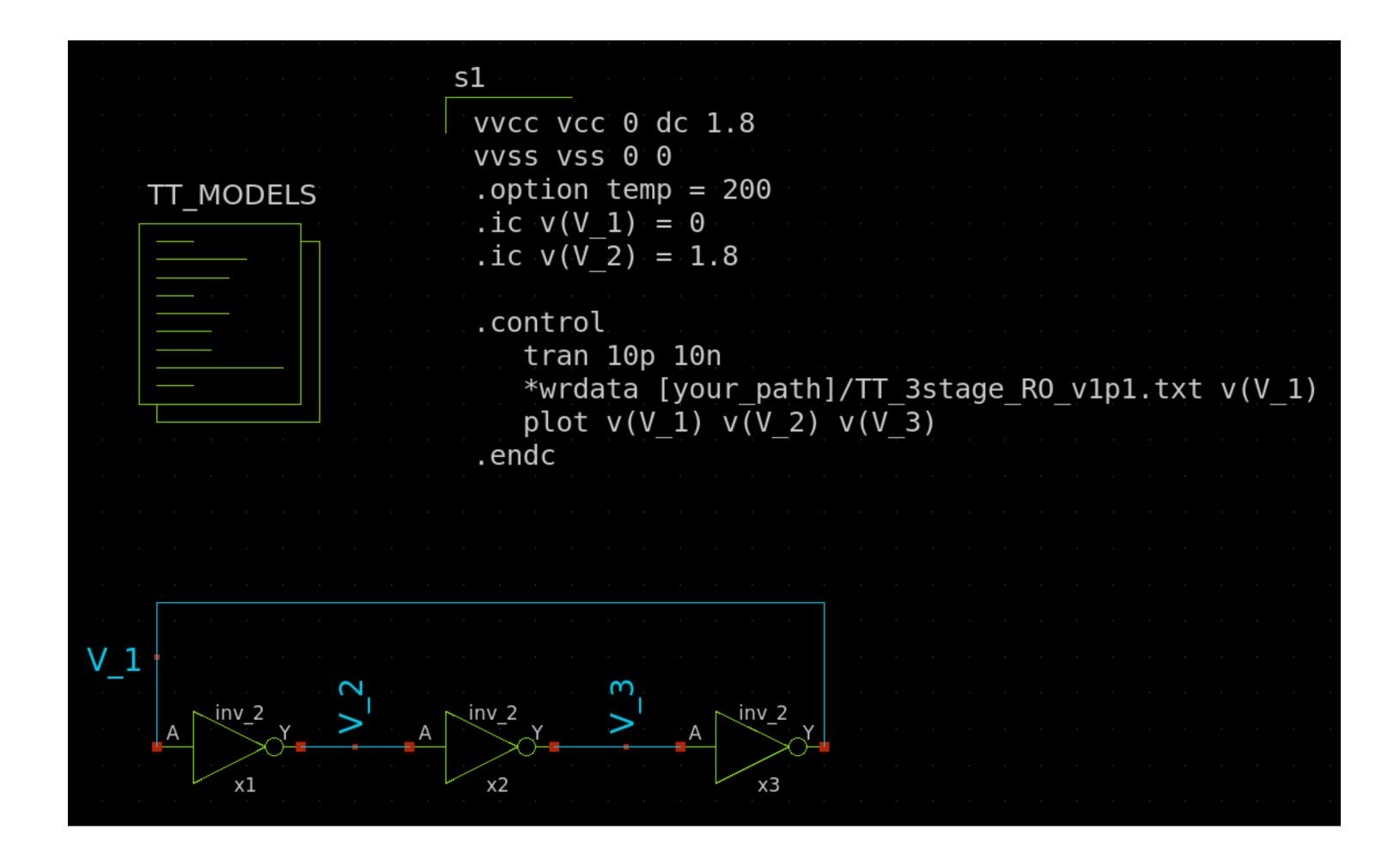

# Example #3: ring oscillator

### • Github link:

https://github.com/JorgeMarinN/UNIC-CASS2024\_AnalogOSIC/blob/main/tb\_3stage\_RO\_UNIC-CASS2024.sch

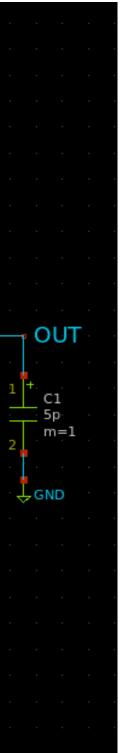

# Example #4: Miller OTA simulation

$$GBW = \frac{gm_{1,2}}{2\pi C_c}$$

$$fnd = \frac{gm_5}{2\pi C_L} \cdot \frac{1}{1 + \frac{C_{n1}}{C_c}} > 3GI$$

**Two** equations for Three variables  $g_{m1}$ ,  $g_{m6}$  and  $C_c$  ?!? Solution : choose  $g_{m1}$  or  $g_{m6}$  or  $C_c$  !!!

[W. Sansen, Analog Design Essentials]

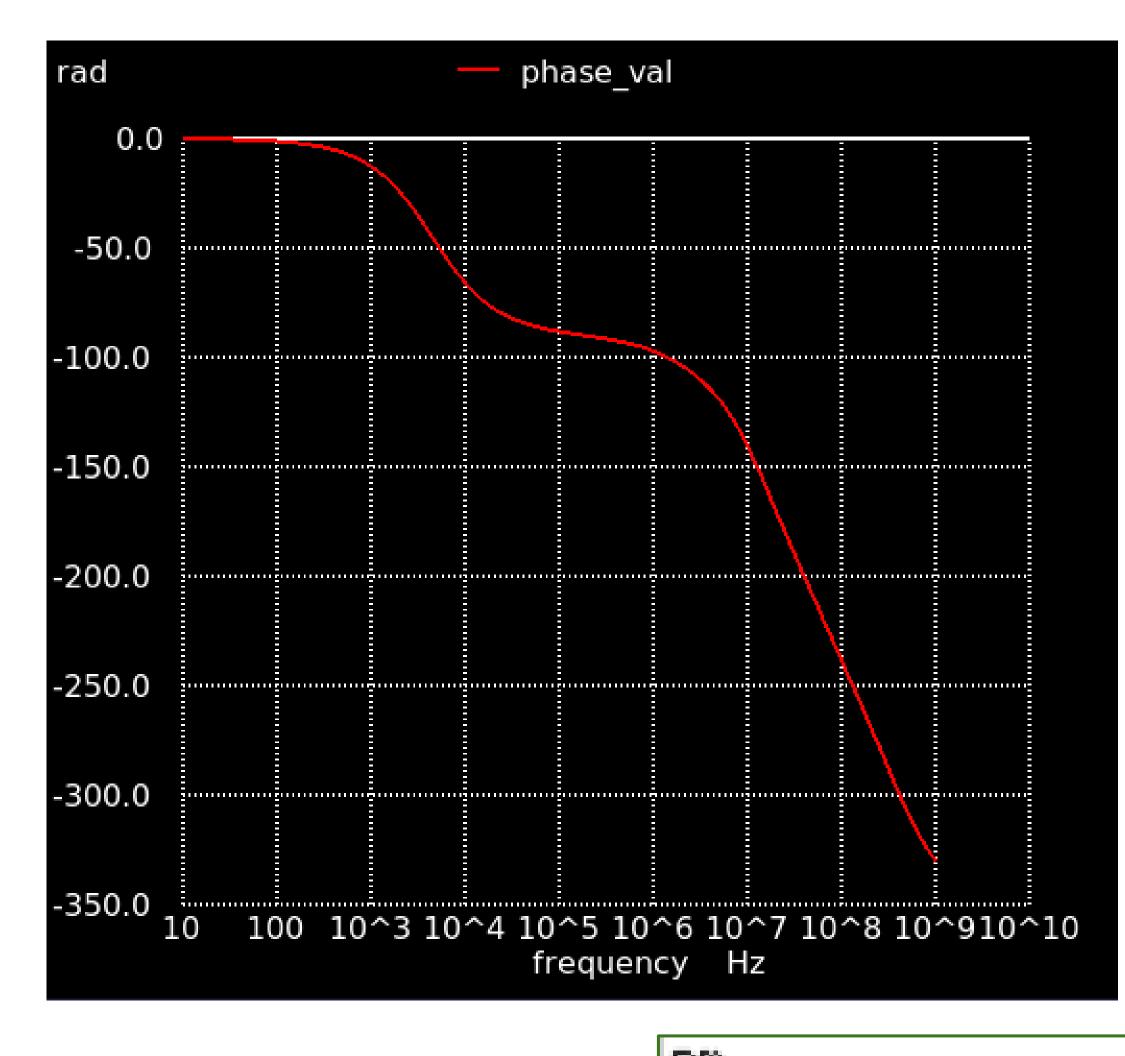

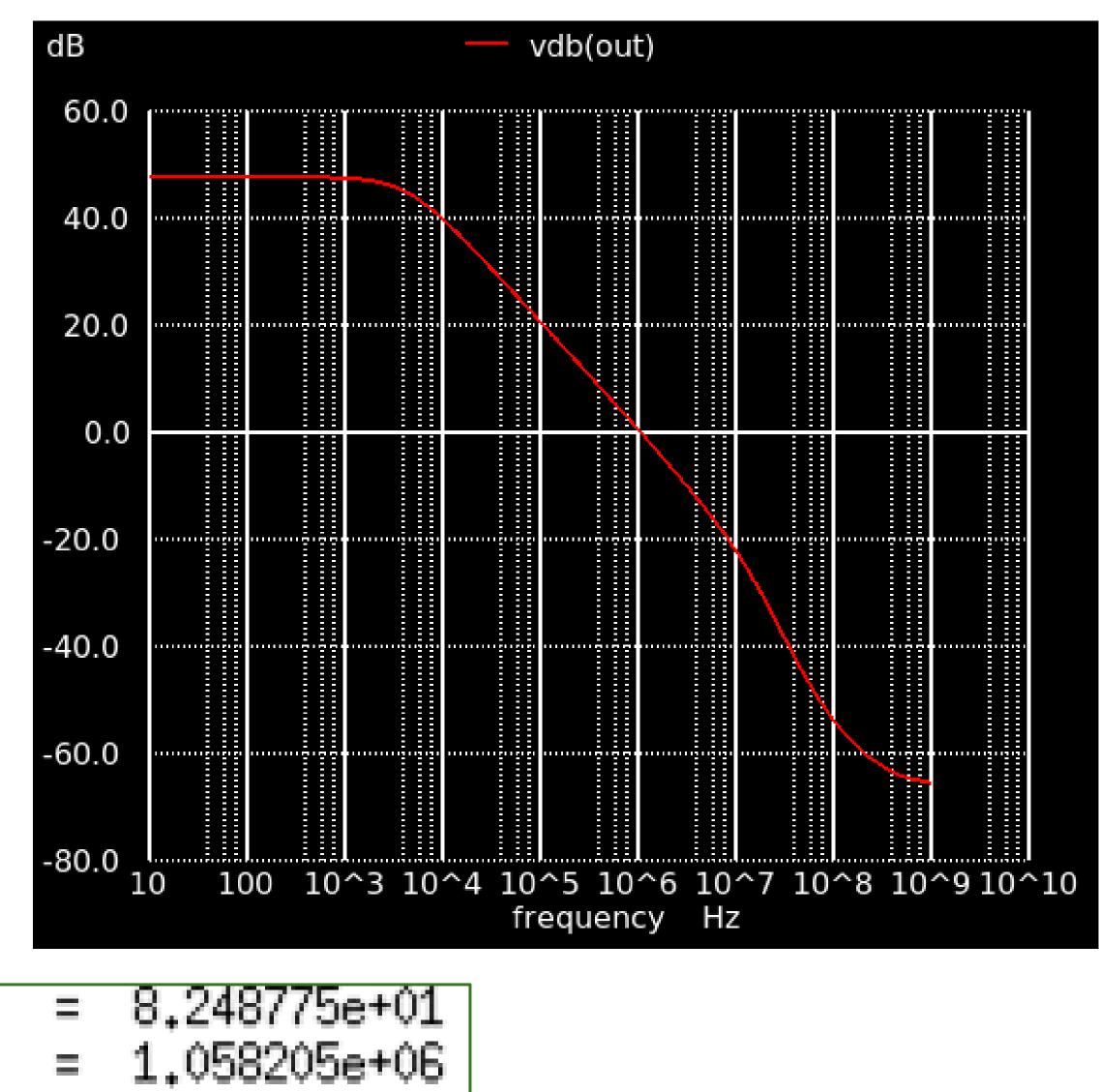

# Example #4: Miller OTA simulation

VDD

### • Github link:

https://github.com/JorgeMarinN/UNIC-CASS2024\_AnalogOSIC/blob/main/tb\_OTA\_stability\_UNIC-CASS2024.sch

#### NGSPICE .param CM VOLTAGE = 0.9.control save all ac dec 200 10 1000Meg settype decibel out plot vdb(out) let phase val = 180/PI\*cph(out) let PM val = 180 + 180/PI\*cph(out)settype phase phase val plot phase val meas ac PM FIND PM val WHEN vdb(out)=0 meas ac GBW WHEN vdb(out)=0 ор

| · · · · · · · · · · · · · · · · · · ·                |         |                                                      |  |

|------------------------------------------------------|---------|------------------------------------------------------|--|

| • • • • • • • • • • • • • • • • • •                  |         |                                                      |  |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$ | VDD VSS | OTA_LASCAS2024<br>x1                                 |  |

| GND · · · · · · · · · · · · · · · · · · ·            |         |                                                      |  |

| → INP · · · · · · · · · · · · · · · · · · ·          | IN_M    |                                                      |  |

| AC 1 · · · · · · · · · · · · · · · · · ·             | IBIAS   |                                                      |  |

| {CM_VOLTAGE}                                         |         | $\begin{array}{cccccccccccccccccccccccccccccccccccc$ |  |

| SND                                                  |         | 1 + 62                                               |  |

|                                                      |         | m=1                                                  |  |

# Example #4: Miller OTA simulation

ΡM gbw

=

#### **Other resources**

# Opensource designs $\rightarrow$ re-use and get inspired

#### Visit: https://platform.efabless.com/projects/public

# SAR ADC

#### Satellite transceiver

#### Logic inverter

#### Sudoku Accelerator

#### **OpenFPGA**

# Opensource designs $\rightarrow$ re-use and get inspired

next-generation Caravel (Chipalooza): vWLQIvP-pCM0lCArM9f1LxhM/edit?gid=0#gid=0

|       | Analog components and specifications 🕁 🙆 👁<br>File Edit View Insert Format Data Tools Extensions Help |                     |                           |                                                                                                                      |

|-------|-------------------------------------------------------------------------------------------------------|---------------------|---------------------------|----------------------------------------------------------------------------------------------------------------------|

| C     | < 母 届 ▼ 100% ▼ ◎ View only                                                                            |                     |                           |                                                                                                                      |

| A1:P1 | 1:P1 • fix Analog IP components and specifications in Sky130A for Efabless next-generation Caravel    |                     |                           |                                                                                                                      |

|       | A                                                                                                     | В                   | С                         | D                                                                                                                    |

| 1     | Analog IP components and specifications in Sky130A for Efabless next-generation Caravel               |                     |                           |                                                                                                                      |

| 2     | Analog components specified for Chipalooza challenge (see additional sheets)                          |                     |                           |                                                                                                                      |

| 3     | IP block                                                                                              | Rank<br>Criticality | Required<br>for ML<br>SoC | URL of Chipalooza challenge submission(s)                                                                            |

| 4     |                                                                                                       |                     |                           |                                                                                                                      |

| 5     | Ultra low-power comparator                                                                            | 2                   | ✓                         | https://github.com/JYSquare2/sky130_icrg_ipulpcomp<br>https://github.com/3x10e8/sky130_rhythmic_ipdynamic_comparator |

| 6     | Comparator                                                                                            | 2                   | $\checkmark$              | https://github.com/Create5517/sky130_pmcm_ip_cmp.git                                                                 |

| 7     | 1.8V Precision bandgap                                                                                | 3                   | $\checkmark$              | https://github.com/adankvitschal/sky130_ak_ipcmos_vref                                                               |

| 8     | Low-power 1.8V LDO                                                                                    | 3                   | √                         | https://github.com/dcdc10893/sky130_deser_ip_lowpowerLDO<br>https://github.com/AlexMenu/sky130_am_ipldo_01v8         |

| 9     | Current reference bias generator                                                                      | 2                   | $\checkmark$              | https://github.com/tatzelbrumm/sky130_cm_ip_biasgen                                                                  |

|       | 40 bit some stiller DAO                                                                               | 1                   | 1                         |                                                                                                                      |

| 10    | 16-bit capacitive DAC                                                                                 |                     | v                         |                                                                                                                      |

# Analog IP components and specifications in Sky130A for Efabless

# https://docs.google.com/spreadsheets/d/132YkMiYaM0iHML5feT1

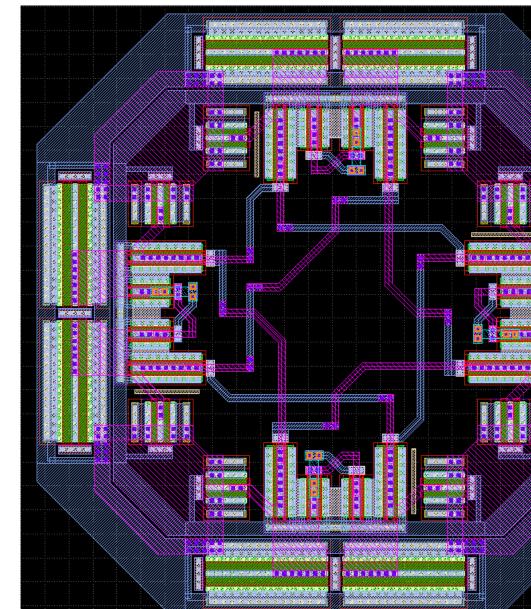

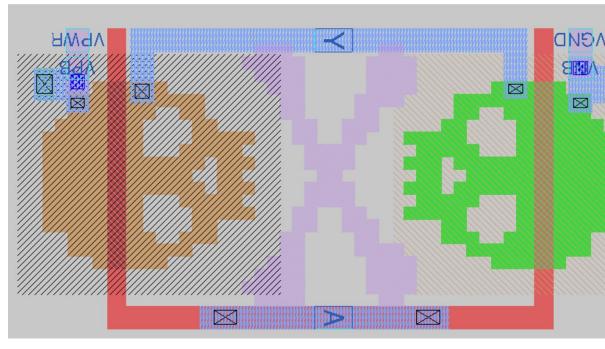

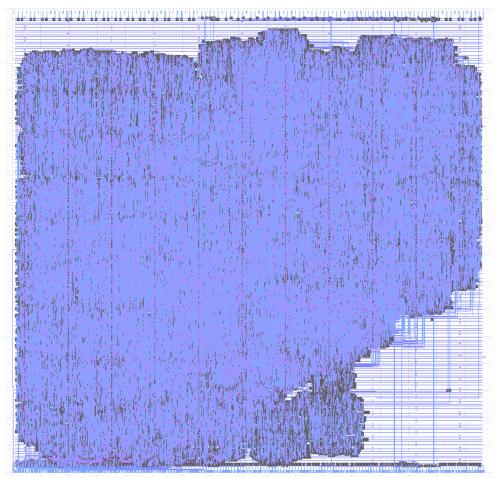

## Code-a-chip notebooks

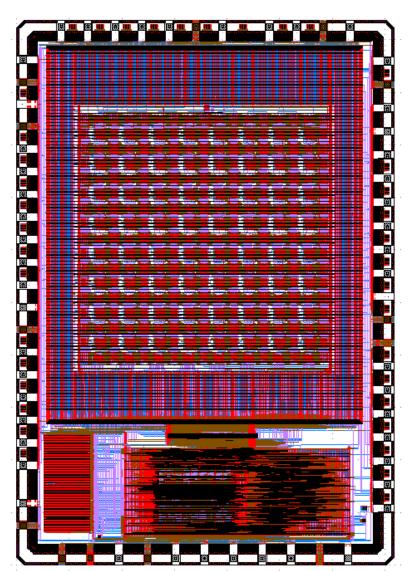

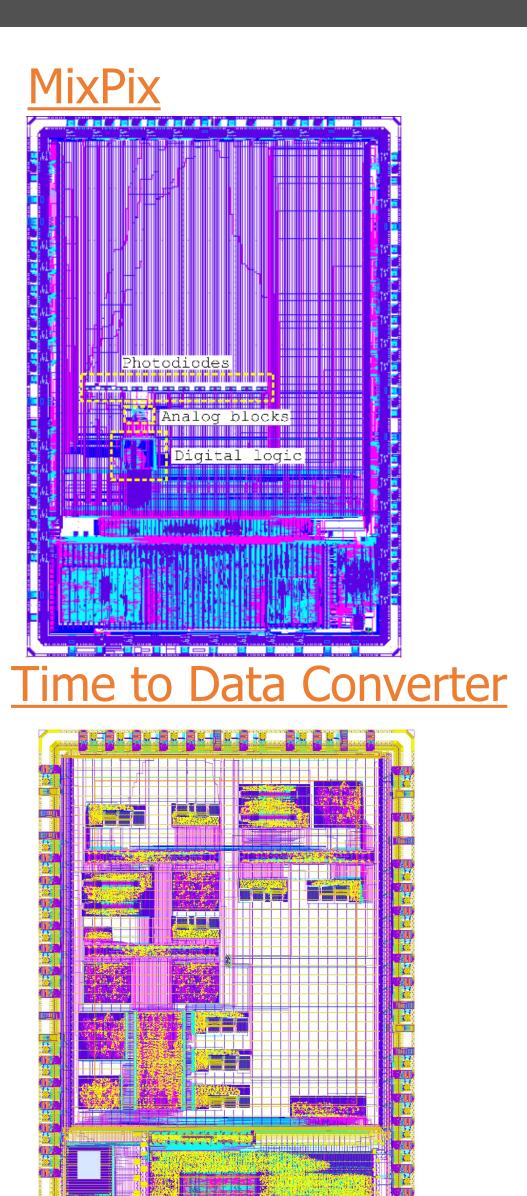

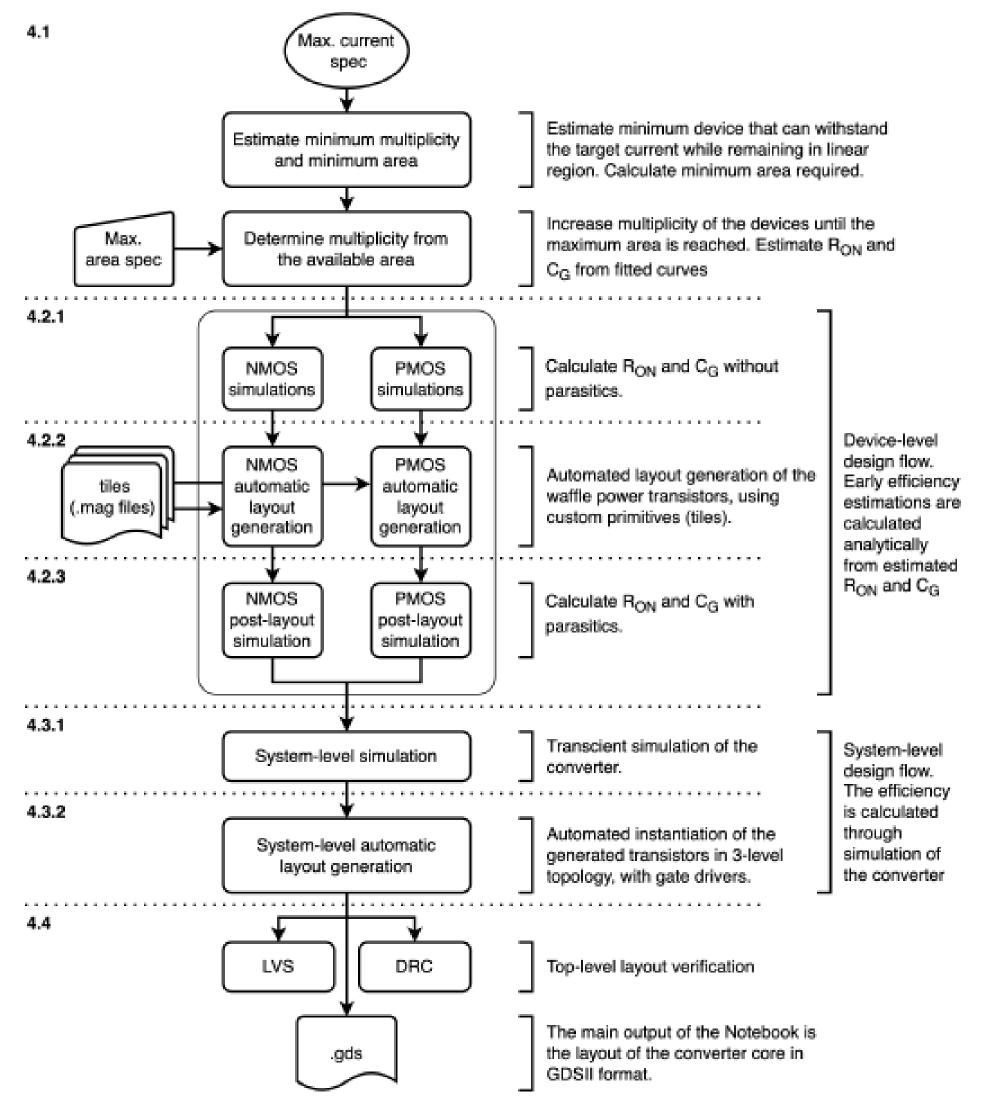

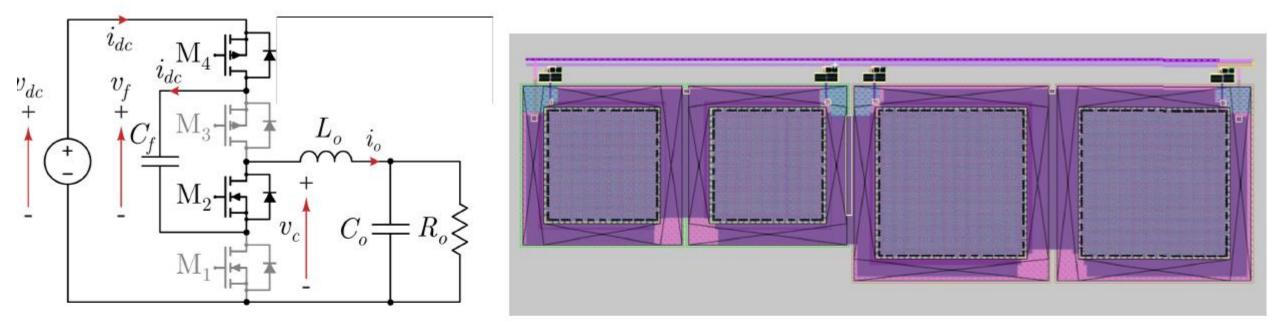

#### Example: https://github.com/sscs-ose/sscs-ose-code-achip.github.io/tree/main/VLSI23/accepted\_notebooks/3LFCC

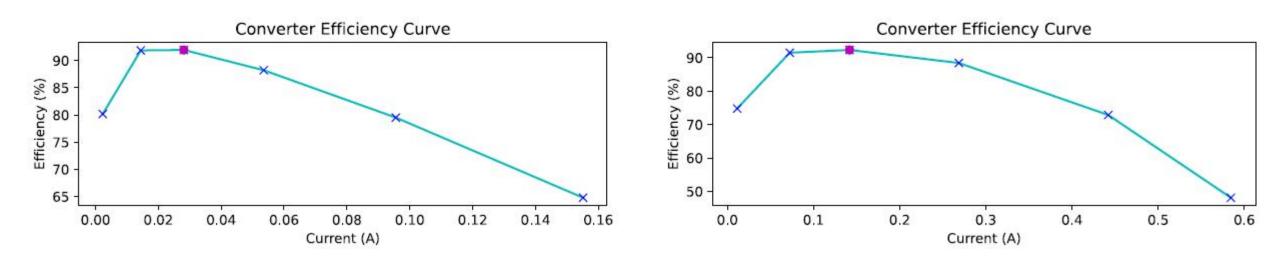

Figure 3: 3LFC Converter schematic (left) and layout (right)

- Full Python-based automated flow using opensource toolkit

- From current, voltage, area and frequency specs to manufacturable layout (GDS file)

### For more information and to join CASS, visit: <u>IEEE-CAS.ORG</u>