#### Introduction to the Opensource Analog Design Flow

Jorge Marin, Postdoctoral Researcher AC3E-UTFSM, Valparaiso, Chile

UNIC-CASS 2023

jorge.marinn@usm.cl

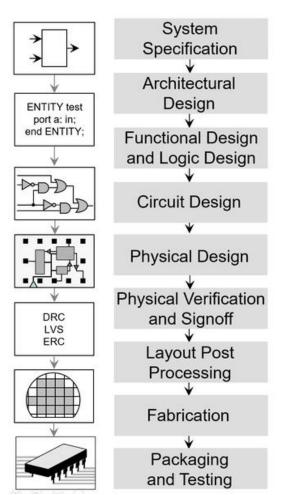

#### Analog vs digital design flows

## ACSE Advanced Center for Liectrical and Electronic Engineering

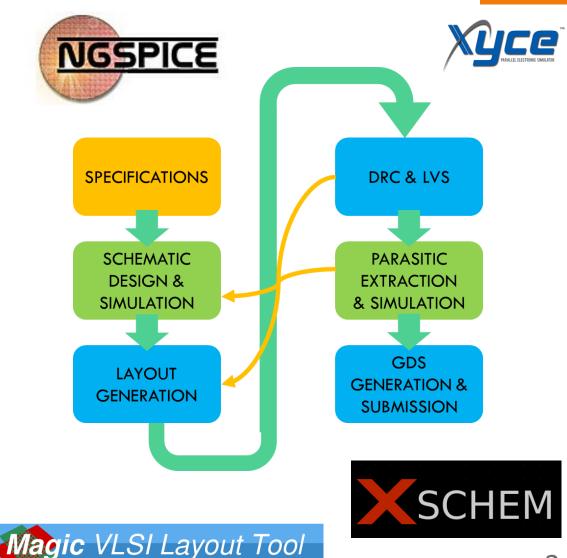

#### **OPENSOURCE EDA TOOLS**

# DIGITAL FLOW

# ш **U**

Current distribution version 8.2

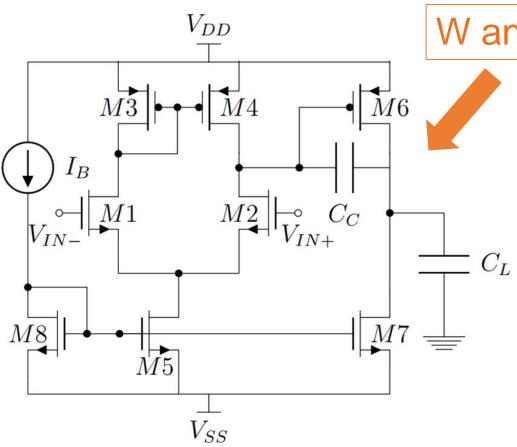

#### Tradeoffs in analog design

W and L for each transistor M1 to M8?

Power Gain

VO Impedance Speed Voltage swing

[B. Razavi]

Analog block example: Miller OTA

Performance is limited by the tradeoff in target specifications

#### Analog design flow environment setup

#### How to get started with design and simulation?

- Environment setup

- Option 1: Analog Mixed Signal Design using docker image & remote desktop

- e.g. IIC-OSIC-TOOLS docker

- Clone at: https://github.com/iic-jku/iic-osic-tools

- Follow detailed instructions

- Option 2: Analog Mixed Signal Design tools on Linux or WSL using Conda

See the environment setup material in the UNIC-CASS page: https://unic-cass.github.io/02-env-setup.html

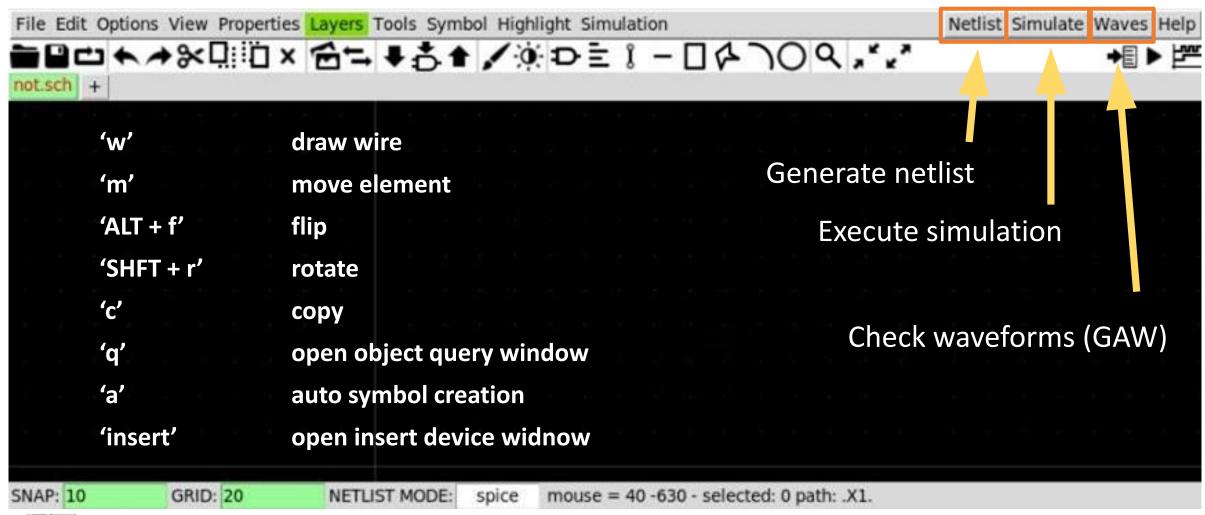

#### Schematic design and simulation

- Relevant tools

- Xschem -> schematic entry and netlist generation

- Ngspice

simulation based on netlist generated by Xschem

- Visualization

- Ngspice window → quick checks

- GAW → integrated in Xschem

- External viewer through raw data (e.g. Python script)

#### Simulation types

- Simulation types

- DC → operating point

- AC → frequency sweep

- Transient  $\rightarrow$  time-domain behavior

- Noise  $\rightarrow$  simulation of device intrinsic noise

- And others...

Ngspice manual will become your best friend! https://ngspice.sourceforge.io/docs/ngspice-manual.pdf

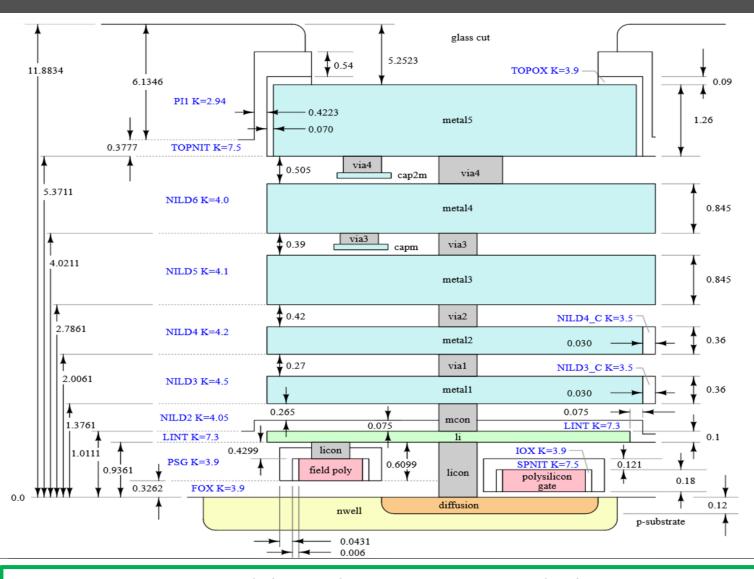

#### Available devices in SKY130

SPICE models inside IIC-OSIC-TOOLS docker:

.lib /foss/pdks/sky130A/libs.tech/ngspice/sky130.lib.spice tt

#### **Device Details**

1.8V NMOS FET

#### Spice Model Information

- Cell Name: sky130\_fd\_pr\_\_nfet\_01v8

- Model Name: sky130\_fd\_pr\_\_nfet\_01v8

Operating Voltages where SPICE models are valid

- $V_{DS} = 0$  to 1.95V

- ullet  $V_{GS}=0$  to 1.95V

- $\bullet~V_{BS}=+0.3$  to -1.95V

Explore

<u>www.skywater-</u>

<u>pdk.readthedocs.io</u>

for device info

#### Example

# Single-transistor DC simulation

For more detailed explanations, explore:

https://unic-cass.github.io/03-analog-design-flow.html#3-analog-design-flow-with-opensource-tools

#### Xschem GUI

#### www.xschem.sourceforge.io

#### Simulation scope

- Nominal

- Ideal simulation without considering many fabrication effects

- P(VT) corners

- Considers global process variation (P) and environment (V, T)

.lib /foss/pdks/sky130A/libs.tech/ngspice/sky130.lib.spice tt

- Mismatch

- Considers local statistical variation among devices

- → See: section 7.7 in https://unic-cass.github.io/07-designexamples.html

- Parasitic extraction/ post layout simulations

Components associated to extrinsic structures (metallization)

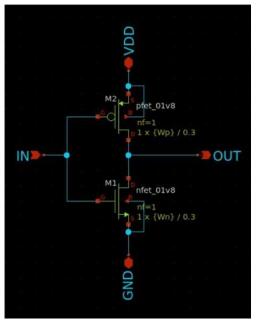

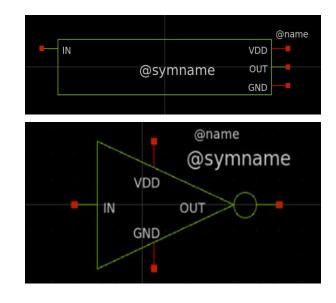

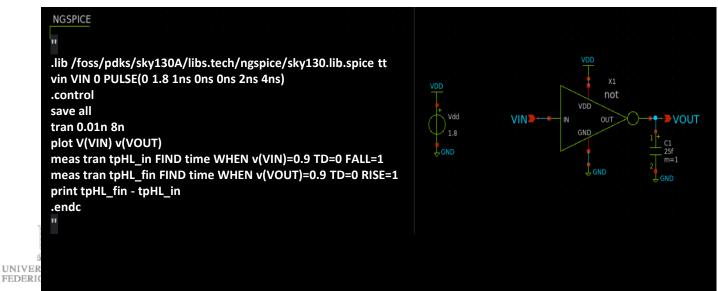

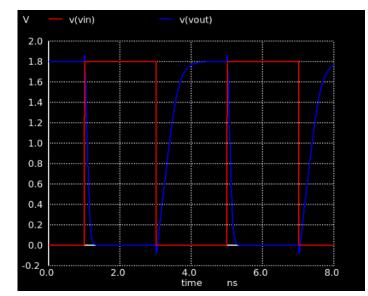

#### Simple inverter example (to be used in Layout later)

#### Simple inverter tutorial

Analog flow tutorial for main flow (in Spanish with subtitles)

Link: https://www.youtube.com/watch?v=6NEOxb7CF6A

#### Opensource designs $\rightarrow$ re-use and get inspired

Visit: https://platform.efabless.com/projects/public

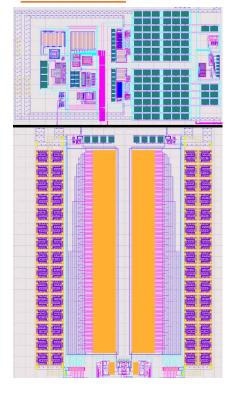

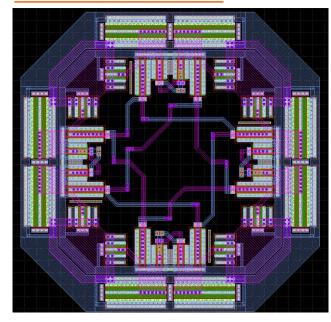

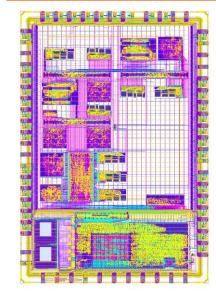

#### SAR ADC

#### Satellite transceiver

#### Logic inverter

#### Sudoku Accelerator

#### **OpenFPGA**

#### **MixPix**

Time to Data Converter

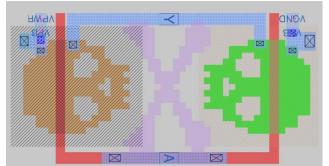

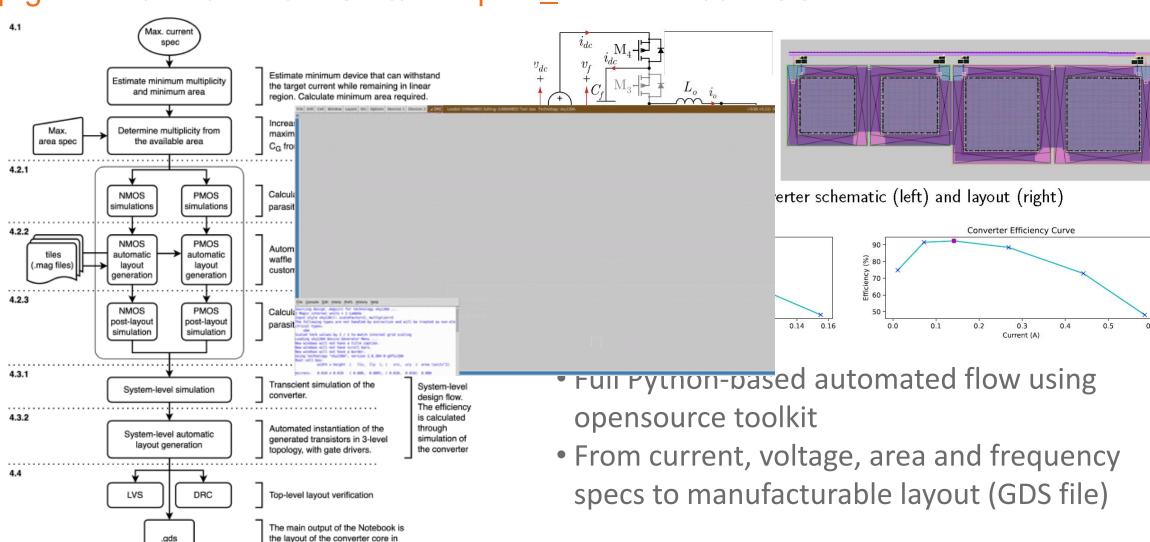

#### Code-a-chip automated power IC specs-to-GDS flow

https://github.com/sscs-ose/sscs-ose-code-a-chip.github.io/tree/main/VLSI23/accepted\_notebooks/3LFCC

GDSII format.

### Thank you

### AC3E

Advanced Center for Electrical and Electronic Engineering

www.ac3e.usm.cl